简介

为什么没有pre?因为pre的题对于我这样的小白来说还是太难了,而且后续也不会重点考察,个人认为没有什么参考价值。

P0是对预习过程中的logisim的强化练习。我觉得可以大概分成两个部分。一部分是执行自定义指令,例如画一个电路图实现一个32位二进制数的某几位的反转。另一部分是状态机的搭建。下面分两部分陈述。

自定义指令

自定义指令的题目其实并不难,主要是考察你对logisim中各种元件的使用。个人觉得比较重要的几个元件有:

- 多路选择器(MUX)

- Splitter

- Bit Extender

- 组合逻辑门(AND, OR, NOT, XOR等)

- 加法器(Adder)

- Bit Selector

- Comparator

以上这些元件在预习过程中应当做到较为熟练地掌握。虽然并不全面,但是足以让你应对P0中的自定义指令题目。在做题时看清题意,按照题目要求一步一步设计即可,不需要过于复杂的设计思路。

状态机设计

状态机的设计有相对固定的套路,只要熟悉了套路状态机简直就在送分。首先要明确的是,状态机分为Moore型和Mealy型两种。Moore型状态机的输出仅与当前状态有关,而Mealy型状态机的输出与当前状态和输入均有关。同一个问题两种设计方式都可以,但是在设计时要根据题目要求选择合适的状态机类型。

理论上来说所有的状态机类型题目都可以用真值表来解决,但是对于某些状态较多的题目来说,真值表会变得非常庞大,不易处理。此时我们可以用正常的逻辑来表示现态到次态的转化以及输出的生成。

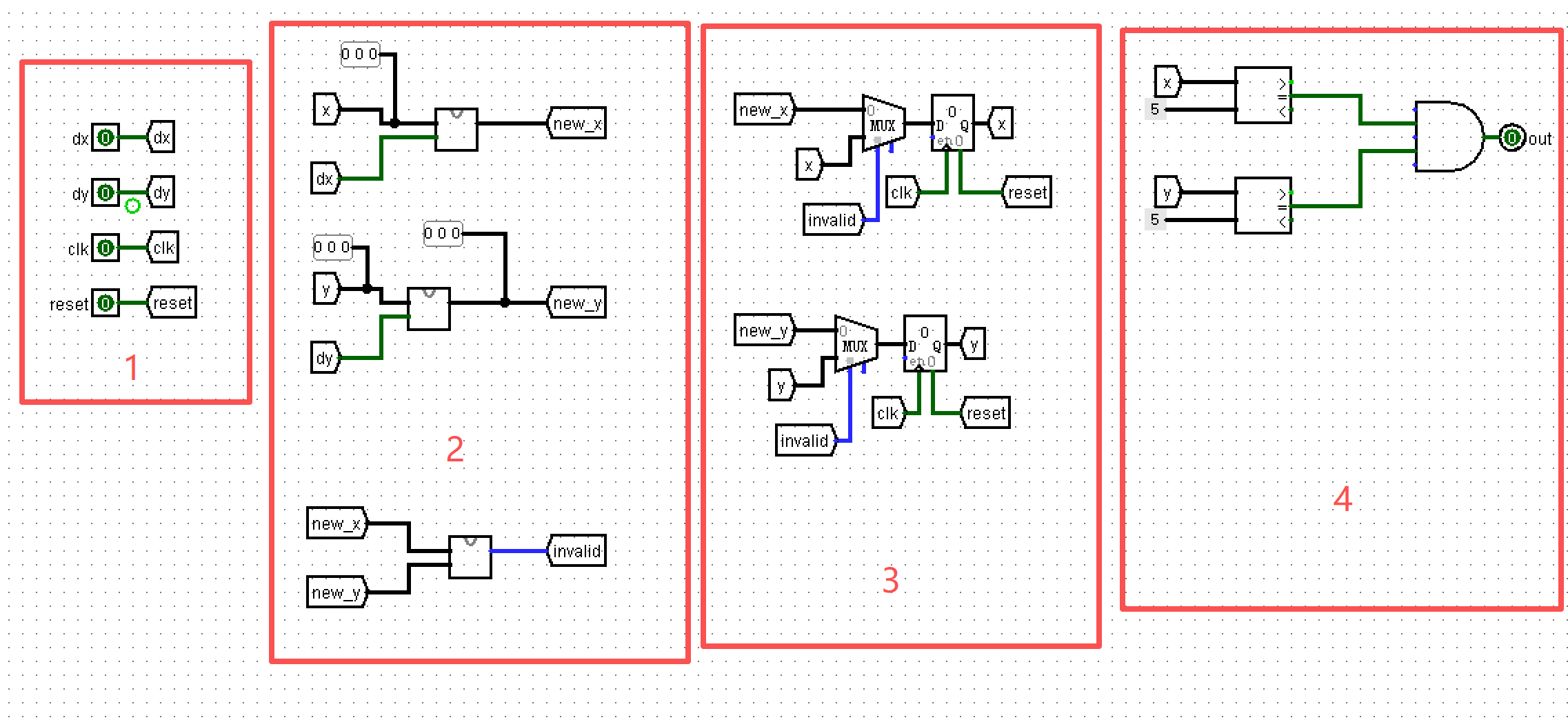

同时,电路图大致可分为4个模块。

- Tunnel Module:负责接收输入信号并进行初步处理。

- calculate next state Module:负责根据当前状态和输入信号计算下一个状态。

- state storage Module:负责存储当前状态,通常使用Register实现。

- output Module:负责根据当前状态和输入信号生成输出信号。

我们以经典的推箱子问题为例说明:大致要求就是从初始状态出发,通过一系列操作将箱子推到目标位置。途中如果碰到障碍物或越界就算失败。

可用真值表表示的状态机

设计时一般遵循以下步骤:

- 明确状态及其编码:这里要根据题目要求确定状态的数量,并为每个状态分配一个唯一的二进制编码。

- 绘制状态转移图:根据题目描述,绘制状态转移图,明确各状态之间的转移关系以及对应的输入条件。

- 编写状态转移表:将状态转移图转换为状态转移表,列出每个状态在不同输入条件下的下一个状态。

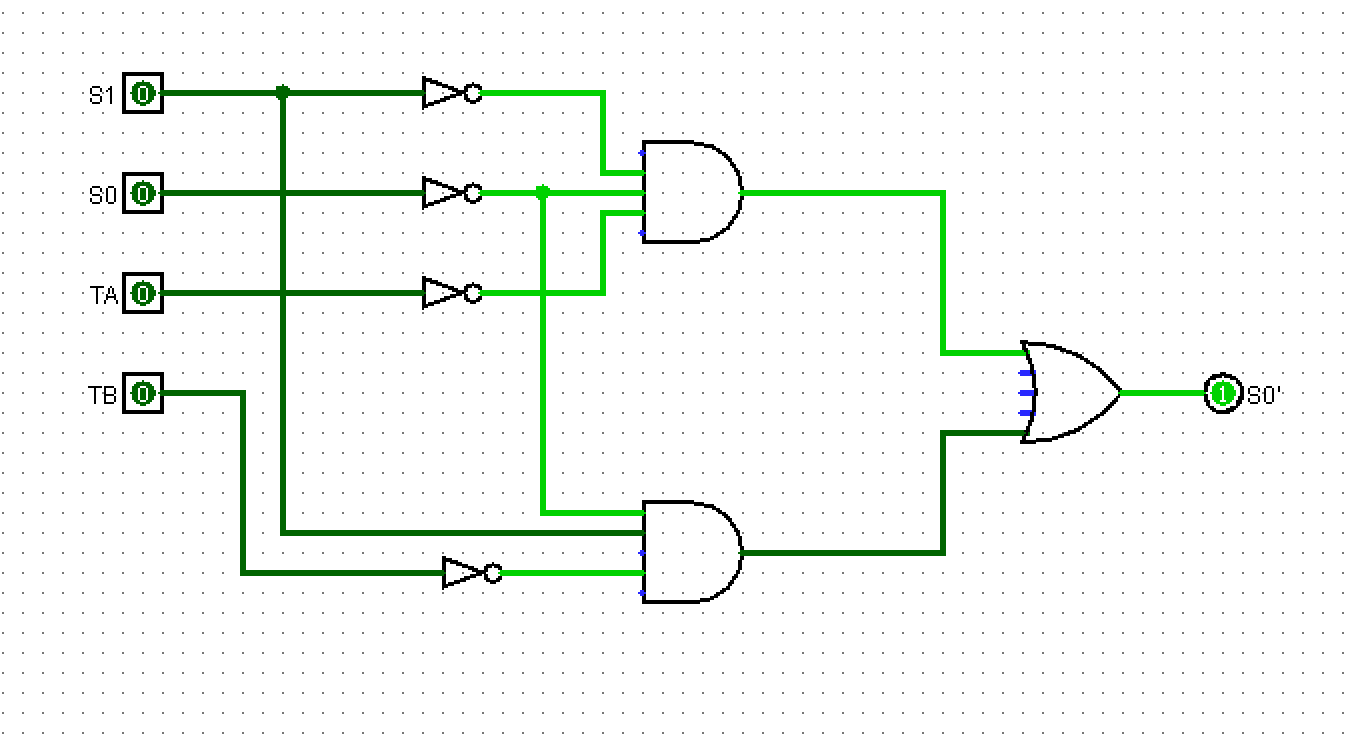

- 设计逻辑电路:根据状态转移表,设计组合逻辑电路来实现状态转移和输出逻辑。这里可以直接利用logisim内置的真值表工具来实现组合电路。具体步骤如下:

project –> Analyze Circuit –> Input & Output & Table –> 填写输入输出变量及真值表 –> Generate Circuit

典型例子有:红绿灯控制器。

输出逻辑计算同理,在此不再赘述。

常规逻辑表达式表示的状态机

设计不便于使用真值表的状态机时,就用最原始的,最正常的逻辑思路来计算下一状态即可。

典型例子有:推箱子。

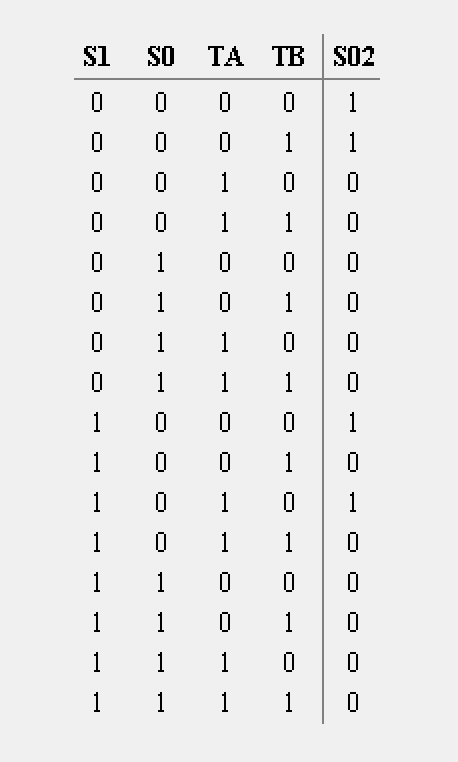

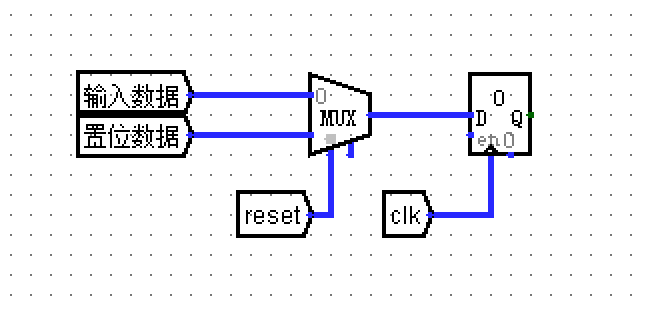

要注意的是次态逻辑的存储时要对次态逻辑的有效性进行判断,例如推箱子中如果出现了碰墙或者越界的情况,次态就不更新,保持不变。这就需要用到多路选择器来选择下一个x到底是x_next还是x_current。

关于Moore型和Mealy型

Moore型和Mealy型的状态转移图有很大区别,因为Mealy型状态机输出不仅和当前状态有关还和输入有关,因此Mealy型状态机中的状态通常比Moore型状态机少一个(少的一般是Moore型状态机的最后一个状态)。这在真值表中体现为输入影响输出,在状态转移图中体现为输出从在方框内表示转化为在边上表示。

如果你使用的是真值表表示方法,那么要修改次态转移逻辑和输出逻辑的真值表。次态转移逻辑减少状态,输出逻辑增加input signal作为输入变量。

如果你使用的是常规逻辑表达式的方法,那么不要动次态逻辑计算的设计,只需要修改输出逻辑的设计即可。输出逻辑要使用next state(注意不是current state,也没有input signal)来作为该板块的输入计算输出。

一些可能的盲区

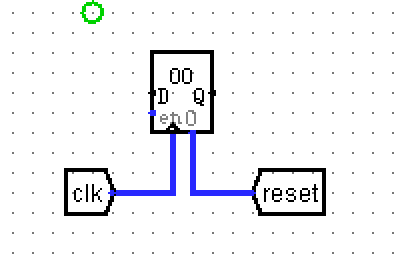

- 异步复位和同步复位:异步复位是指复位信号一旦被触发,无论时钟信号的状态如何,电路都会立即进入复位状态。而同步复位则是指复位信号只有在时钟信号的上升沿(或下降沿)到来时才会生效。在设计状态机时要根据题目要求选择合适的复位方式。他们的实现方式也不尽相同。

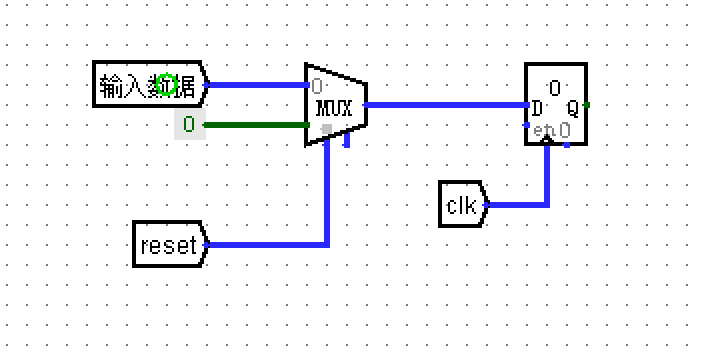

- “异步”置位和同步置位:同步置位则是指置位信号只有在时钟信号的上升沿(或下降沿)到来时才会生效。而“异步”置位跟字面意思不太一样,我们要求

reset信号在clk信号为低电平时拉高,在clk信号高电平时接地,同时要求clk信号为高电平时能够在register中存储reset信号为高电平时希望设置的值。同步置位的实现方式和同步复位的方式类似,但是“异步”置位的实现就和异步复位大不相同了。

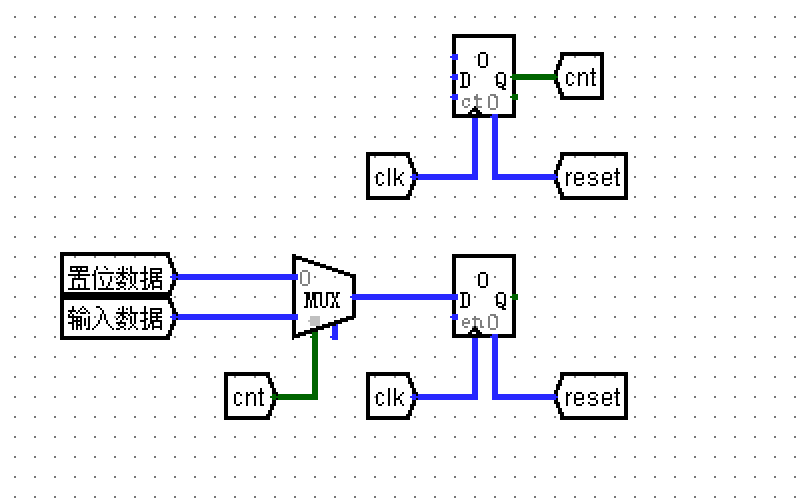

因为reset信号的转瞬即逝,我们希望有某个模块可以留住reset的效果,Counter成为了最佳选项。电路连接如下图:

我们将Counter模块的Data bits设置为1位,Action on overflow设置为Stay at value,再将cnt作为选择信号来选择存入register的数据来源。我们分析可以得出,当reset为低电平时,除了初态,所有的状态cnt均为1。当reset为高电平时,cnt变为0。即使此时reset信号转为低电平,cnt依然保持0。因此在clk上升沿时,register模块存入的数据始终为x,从而实现了“异步”置位的效果。

同步置位就很简单了,如下图:

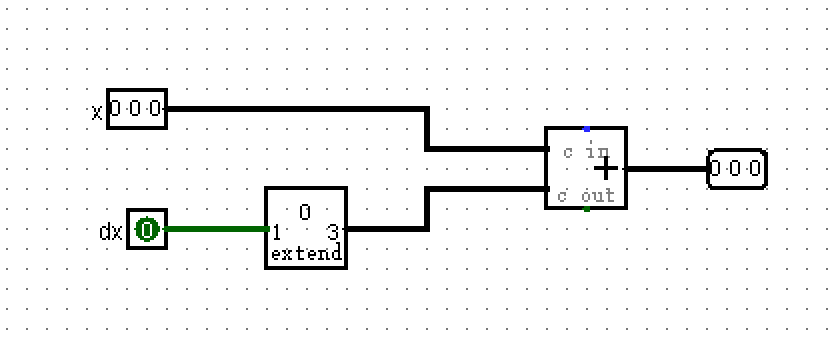

- 多个数比大小

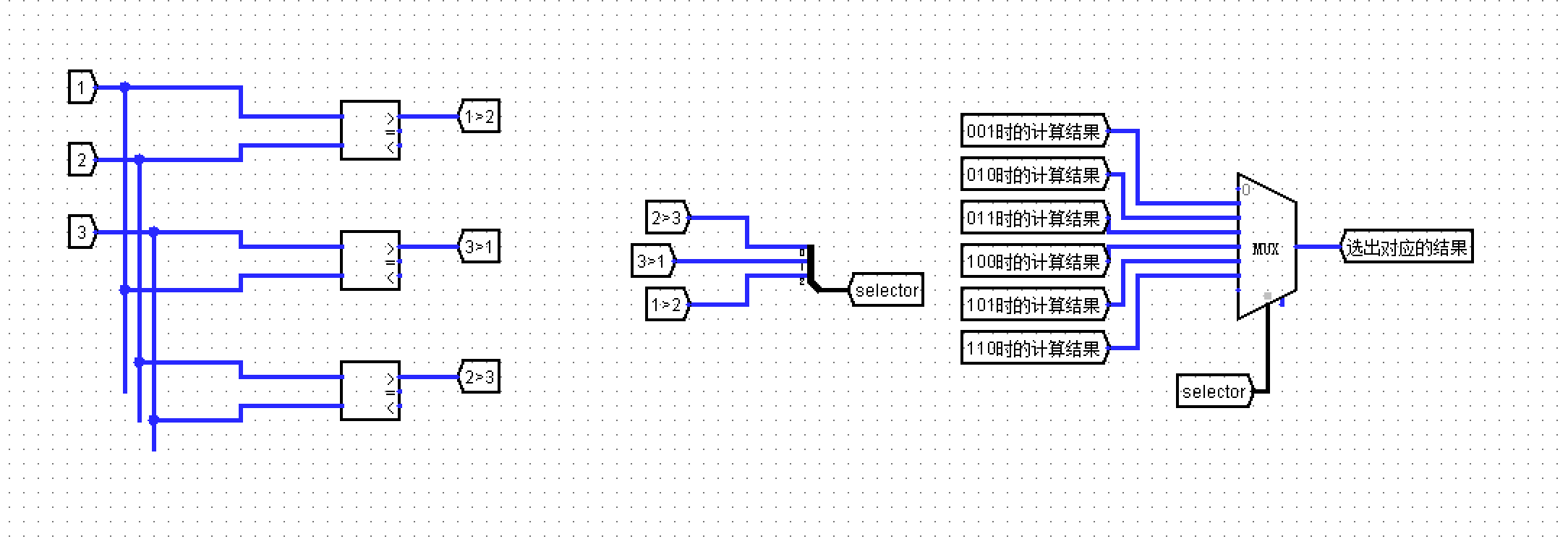

在设计多个数比大小的逻辑时,可以使用多个Comparator模块进行两两比较,然后将比较结果进行综合处理。这里需要用到分类讨论的知识。分类讨论的结果可以可以作为多路选择器的待选择信号,比较结果可以作为选择信号,从而实现不同情况下的输出。

Lyrics Sharing

你身边的那位 |